CISC and RISC, both are instruction set-based microprocessors. RISC stands for Reduced Instruction Set Computer and CISC stand for Complex Instruction Set Computer. Here in this article, we have shared the comparison and difference between CISC and RISC.

⦿ Difference between CISC and RISC

First of all, we will give you a basic idea about what is CISC and RISC then we will compare both and make points on the difference between CISC and RISC.

► What is CISC? (RISC and CISC Difference)

The full form of CISC is Complex Instruction Set Computer. CISC is a computer in which single instructions can execute several low-level operations (such as a load from memory, an arithmetic operation, and a memory store) or are capable of multiple operations or addressing modes within a single instruction.

► What is RISC? (RISC and CISC Difference)

The full form of RISC is Reduced Instruction Set Computer. RISC is a computer that only uses simple instructions that can be divide into multiple instructions which perform the low-level operation with a single clock cycle.

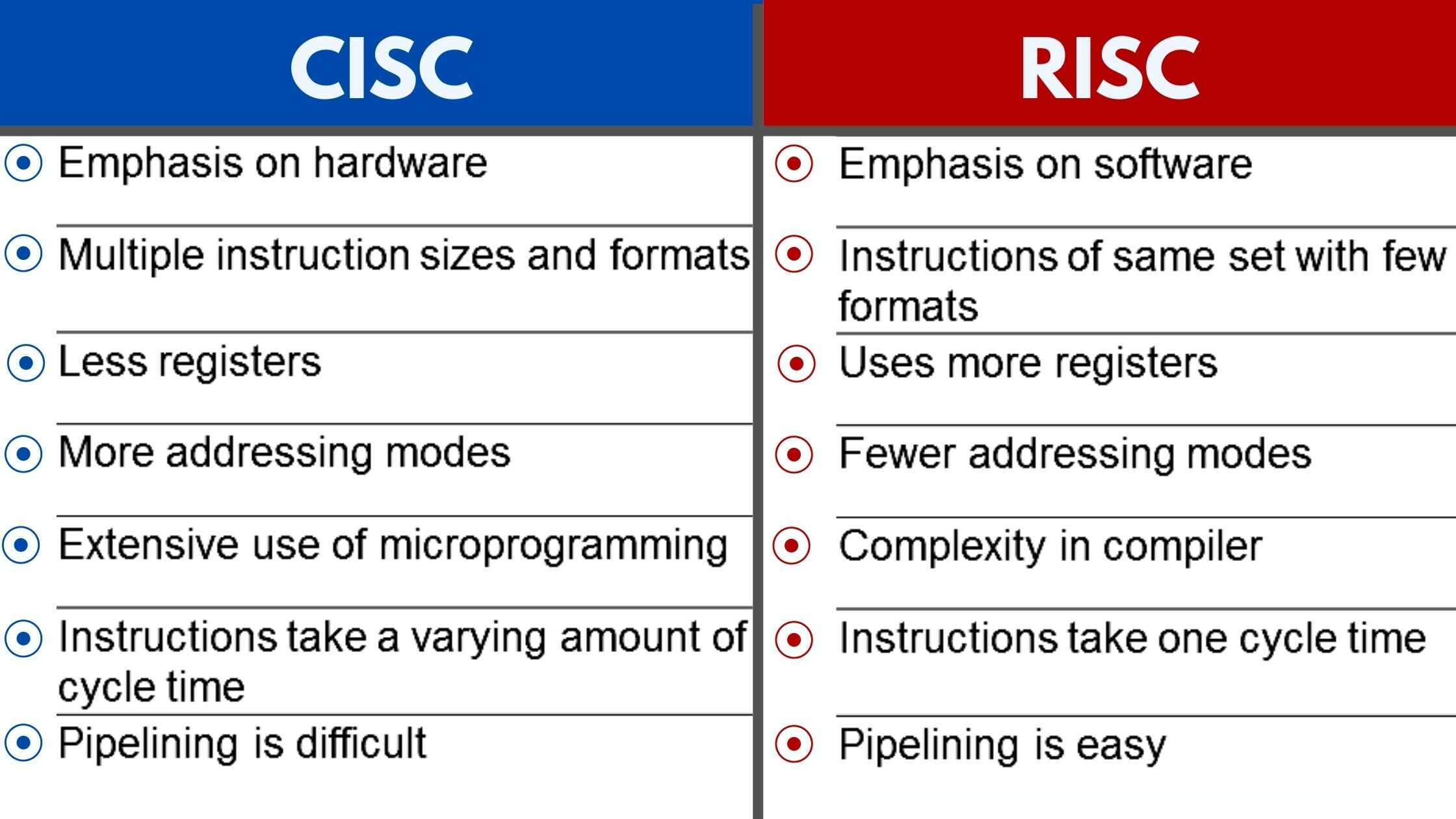

► Difference between CISC and RISC

⦿ History of CISC and RISC Processors

Jack Kilby created the first integrated chip in 1958. Microprocessors were originally launched in the 1970s, with Intel Corporation producing the first commercial microprocessor.

The RISC architecture was introduced in the early 1980s. Because the CISC architecture was becoming more sophisticated, the RISC design was created as a complete overhaul.

Most people credit IBM’s John Cocke with inventing the RISC concept.

According to history, in order to create a faster computer, certain fundamental improvements in microprocessor architecture occurred, resulting in RISC, which included a standardized syntax for instructions and the ability to efficiently pipeline operations.

(The term “pipelining” refers to the fact that the processor begins executing the next instruction before the current one is completed.) Because memory was expensive in the 1970s, smaller programs were prioritized.

Must Read ➜ What is HTTP?

RISC and CISC Difference

Let’s learn about the difference between RISC and CISC in a detailed manner one by one.

⦿ RISC Microprocessor

Reduced Instruction Set Computer Processor (RISC) is a microprocessor architecture with a small set of instructions that can be substantially modified.

It is designed to reduce the time it takes for instructions to execute by optimizing and reducing the number of instructions.

It means that each instruction cycle only takes one clock cycle and has three parameters:

- Fetch,

- Decode, and

- Execute.

The RISC processor can also be used to combine multiple complex instructions into a single one. RISC chips require several transistors, making them less expensive to develop and reducing instruction execution time.

SUN’s SPARC, PowerPC, Microchip PIC CPUs, and RISC-V are examples of RISC processors.

► RISC Architecture (Reduced Instruction Set Computing)

It is a highly specialized set of instructions used in portable devices such as Apple iPod, mobile phones/smartphones, Nintendo DS, and others due to system stability.

► Characteristics of RISC Processor:

The following are some key characteristics of RISC processors:

One cycle execution time:

RISC processors require one CPI to execute each instruction in a computer (Clock per cycle). Each CPI also comprises the methods for fetching, decoding, and executing computer instructions.

Pipelining approach:

In RISC processors, the pipelining approach is used to execute many sections or stages of instructions in order to function more efficiently.

Several registers:

RISC processors are designed with multiple registers that can be utilized to store instructions, respond fast to the computer, and reduce memory interaction.

- For pipeline execution, it supports a simple addressing mode and a fixed length of the instruction.

- To access the memory location, it employs the LOAD and STORE instructions.

- In a RISC, a process’ execution time is reduced by using simple and constrained instructions.

► Advantages of RISC Processor

- Because the RISC processor’s instruction set is simple and constrained, its performance is better.

- It necessitates the use of multiple transistors, which makes it less expensive to design.

- Because of its simplicity, RISC allows instructions to utilize spare space on a CPU.

- Because of its simple and speedy architecture, a RISC processor is simpler than a CISC processor, and it can finish its task in one clock cycle.

► Disadvantages of RISC Processor

- Because following instructions in a cycle may rely on the prior instruction for execution, the RISC processor’s performance may vary depending on the code executed.

- Complex instructions are frequently used by programmers and compilers.

- To preserve various instructions that require a huge collection of cache memory to react to the instruction in a short time, RISC processors require very fast memory.

Must Read ➜ What is Cyclic Redundancy Check (CRC)?

⦿ CISC Microprocessor

The Intel-developed CISC stands for Complex Instruction Set Computer. It has a huge number of sophisticated instructions, ranging from simple to extremely complicated and specialized at the assembly language level, which takes a long time to execute. As a result, CISC addresses each program by lowering the number of instructions while ignoring the number of cycles per instruction.

Because hardware is always quicker than software, it promotes writing complex instructions directly in hardware. CISC chips, on the other hand, are slower than RISC chips, although they consume fewer instructions. VAX, AMD, Intel x86, and the System/360 are examples of CISC processors.

► Characteristics of CISC Processor

The following are the RISC processor’s primary characteristics:

- Because the code is brief, it only uses a little amount of RAM.

- The execution of CISC or complicated instructions may take more than one clock cycle.

- Writing an application requires less instruction.

- It makes assembly language programming easy.

- Support for complicated data structures and high-level language compilation.

- It has fewer registers and more addressing nodes, usually between 5 and 20.

- Instructions can be more than one word long.

- It focuses on the creation of instructions on hardware rather than software because the hardware is faster to develop.

► CISC Architecture (Complex Instruction Set Computer)

By incorporating several operations on each program instruction, the CISC design helps decrease program code while also making the CISC processor more complex.

Because large programs or instructions require a big amount of memory space to store data, the CISC architecture-based computer is designed to reduce memory costs.

A huge collection of memory raises the memory cost, making them more expensive.

► Advantages of CISC Processors

There are many advantages and benefits of CISC.

- In CISC processors, the compiler converts high-level programs or statement languages into assembly or machine code with little effort.

- The code is relatively small, which reduces the amount of memory required.

- It takes extremely little RAM to store the instructions on each CISC.

- The execution of a single instruction necessitates the completion of multiple low-level activities.

- CISC develops a power management technique that modulates clock speed and voltage.

- It employs a less number of instructions to do the same task as RISC.

► Disadvantages of CISC Processors

- CISC chips run per instruction cycle on each program slower than RSIC chips.

- Because the clock speed is too sluggish, the machine’s performance suffers.

- The CISC processor’s execution of the pipeline makes it difficult to use.

- In comparison to RISC circuits, CISC chips require more transistors.

- In CISC, only 20% of existing instructions are used in a programming event.